NVIDIA Jetson TX2 - Diving deep into video Input system and camera image capture latency.

- ridgerun

- Dec 4, 2019

- 1 min read

Updated: Sep 9, 2020

This blog from RidgeRun engineering team throws some light on the Jetson TX2 Video Input (VI) system and its relevant building blocks comes into picture during latency evaluation purposes.

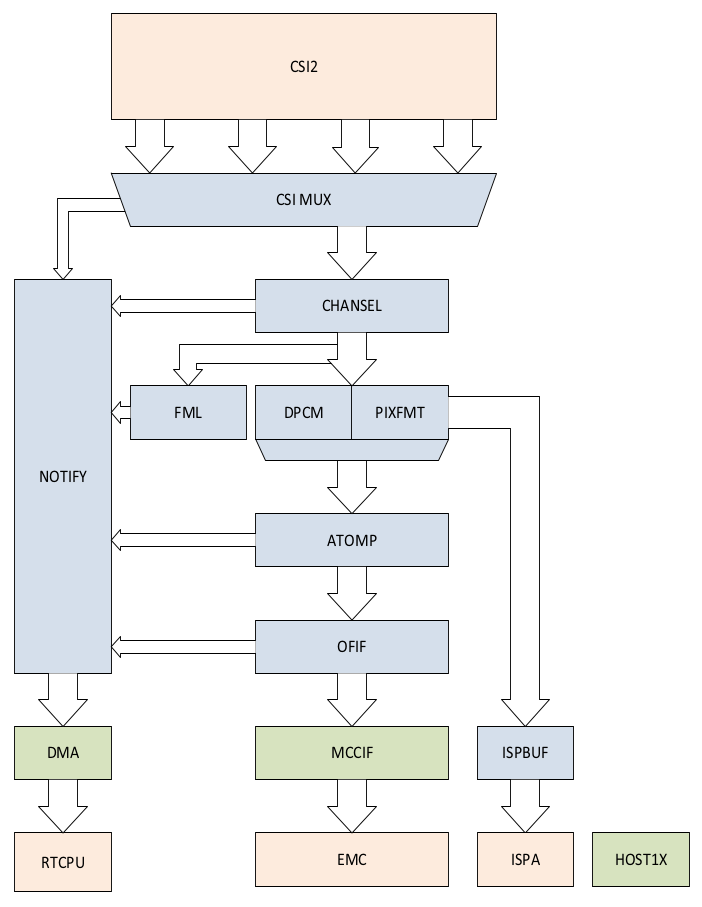

Top level diagram of the Video Input system and latency relevant blocks:

For latency evaluation purposes, the CHANSEL, ATOMP, NOTIFY, RTCPU, ISP and ISPBUF blocks are important.

Definitions:

In addition to these blocks, following are the details applied during latency evaluation purposes:

Timestamping System Clock : The clock used to timestamp the events emitted by the VI is TSC (TimeStamp Counter).

Capture Paths :

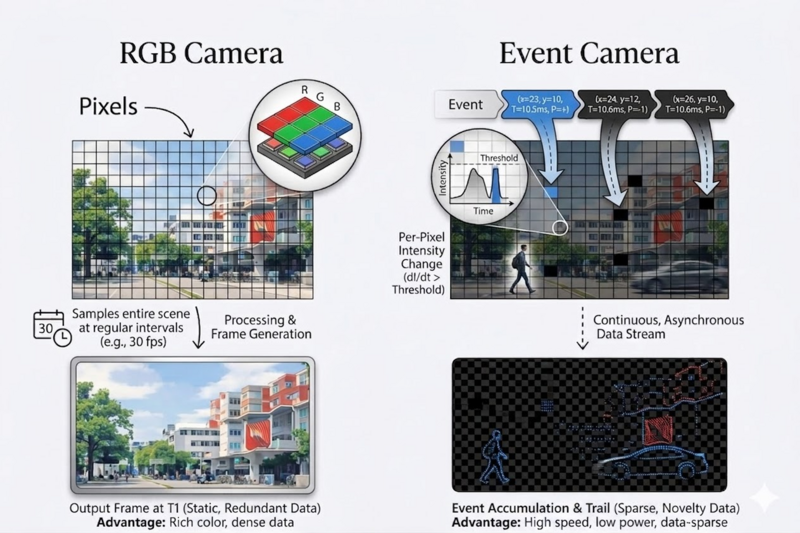

The path of the pixel data is different depending on the mechanism used to capture images. There are two paths often used: Path with ISP and Path without ISP (The image signal processor also called ISP or ISP4).

More technical details are explained in the RidgeRun developer wiki page : NVIDIA Jetson TX2 - Video Input Timing Concepts

Contact Us

Please visit our Main Website for the RidgeRun online store or Contact Us for pricing information of the engineering support, product and Professional Services.

Please email to support@ridgerun.com for technical questions and for an evaluation version (if available).

Contact details for sponsoring the RidgeRun GStreamer projects are available at Sponsor Projects page.